FPGA動的再配置(FPGA版プラグイン機能)《実装と動作確認・付録》

1/3《概要・開発概要》 2/3《検討・実装方法》 3/3《実装と動作確認・付録》

5. サンプルの実装と動作確認

5.1. サンプル・ユーザIPとしての前処理ブロック

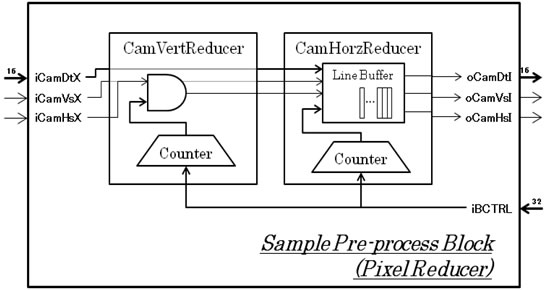

動的再配置をする前処理ブロックのサンプルとして、間引き前処理ブロックを設計、実装した。間引き前処理ブロックは、カメラから入力される画像のピクセルを間引いて縮小した画像を出力する。FPGAの基本機能ブロックからは、本来接続されているカメラより小さいサイズの画像を出力するカメラが接続されているように認識して動作をする。以下に間引き前処理ブロックの概略図を示す。

外部入力として、カメラからの標準的な画像信号(データ/垂直同期/水平同期)を取り込みながら、ピクセルを間引いて縮小した画像を内部に出力する。iBCTRLポートは、間引く量を指定するためのパラメータ入力である。CamVertReducerブロックは、カウンタの値により水平同期信号に関して1ライン全体をゲートすることで、垂直方向のラインを間引く。

CamHorzReducerブロックは、1ライン中のピクセルに関してカウンタ値により必要なデータと同期信号だけLine-Bufferに格納することで、水平方向のピクセルを間引く。内部への出力時、oCamHsIアサートで間引いたデータを間断なく出力するためにLine-Bufferが必要となる。間引き前処理ブロックのHDLソースを本レポートの付録として、末尾に掲載する。

●FPGAの動的再配置により、再配置された間引きサンプル前処理ブロックに対して、ホストPCアプリのSVIsamを使用してパラメータを送信し、画像取り込み動作でホストPCに表示される取り込み画像が間引かれて縮小表示されることを確認した。

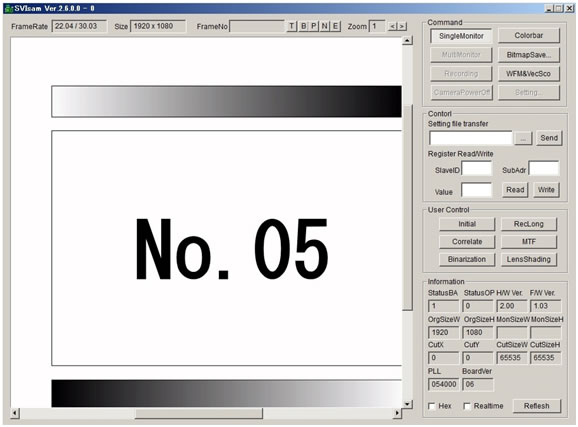

下図は、間引き前処理ブロックのユーザIPを入れない基本機能のみのFPGAで動作させた場合での、SVIsamアプリ実行画面の様子である。1080p(1920x1080プログレッシブ)の画像がそのまま取り込まれて表示されている。

CamHorzReducerブロックは、1ライン中のピクセルに関してカウンタ値により必要なデータと同期信号だけLine-Bufferに格納することで、水平方向のピクセルを間引く。内部への出力時、oCamHsIアサートで間引いたデータを間断なく出力するためにLine-Bufferが必要となる。間引き前処理ブロックのHDLソースを本レポートの付録として、末尾に掲載する。

5.2. 動作確認

●FPGAの動的再配置の第一段階として、SVI-06ボードの電源をON/OFFすることなしに、ホストPCアプリのSVIUpdateを使用して、FPGAの内容を入れ替えて、立ち上がることを確認した。●FPGAの動的再配置により、再配置された間引きサンプル前処理ブロックに対して、ホストPCアプリのSVIsamを使用してパラメータを送信し、画像取り込み動作でホストPCに表示される取り込み画像が間引かれて縮小表示されることを確認した。

下図は、間引き前処理ブロックのユーザIPを入れない基本機能のみのFPGAで動作させた場合での、SVIsamアプリ実行画面の様子である。1080p(1920x1080プログレッシブ)の画像がそのまま取り込まれて表示されている。

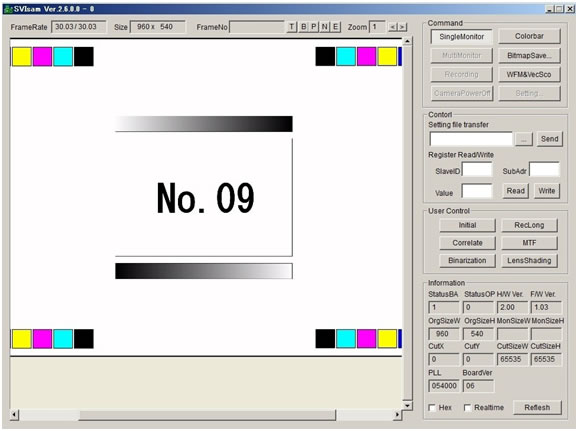

次の図は、前述と同じ画像入力に対して、SVIUpdateアプリによってFPGAを動的再配置し、間引き前処理ブロックのユーザIPを実装して動作させた場合での、SVIsamアプリ実行画面の様子である。1080p(1920x1080プログレッシブ)画像入力に対して、Sizeが縦横1/2に間引きされた画像(960x540)で取り込まれて表示されている。