# CXD4960ER-W GVIF2 デシリアライザ基板 (GVI-4960 / NV017-D) ハードウェア仕様書

第4版

株式会社ネットビジョン

## GVIF2 デシリアライザ基板 (NV017-D) ハードウェア仕様書 第4版

## 改訂履歴

| 版数  | 日付         | 内容                          | 担当 |

|-----|------------|-----------------------------|----|

| 第1版 | 2021/06/15 | 初版作成                        | 山田 |

| 第2版 | 2022/02/28 | 半田面の基板寸法図を修正                | 山田 |

|     |            | コネクター覧表の型番を修正               |    |

| 第3版 | 2022/04/08 | コネクタ一覧表の CN5,CN6 のコネクタ番号を修正 | 山田 |

| 第4版 | 2023/11/22 | GVI-4960-F の写真を掲載           | 三島 |

|     |            |                             |    |

# 目次

| 1. |       | 概要3           |   |

|----|-------|---------------|---|

| 2. |       | 基板形状4         |   |

|    | 2.1.  | コネクタ配置図       |   |

|    | 2.2.  | 基板写真5         |   |

| 3. |       | 詳細6           | , |

|    | 3.1.  | GVIF2 入力6     | i |

|    | 3.2.  | PoC 回路6       |   |

|    | 3.3.  | GVIF2 出力      |   |

|    | 3.4.  | 電源7           |   |

|    | 3.5.  | 12C バス、GVIFID |   |

|    | 3.6.  | コネクター覧表       |   |

|    | 3.7.  | コネクタ詳細        |   |

|    | 3.8.  | スイッチ 11       |   |

|    | 3.9.  | ジャンパ設定11      |   |

|    | 3.10. | . LED インジケータ  |   |

| 4. |       | 主要諸元12        |   |

| 5. |       | Appendix      |   |

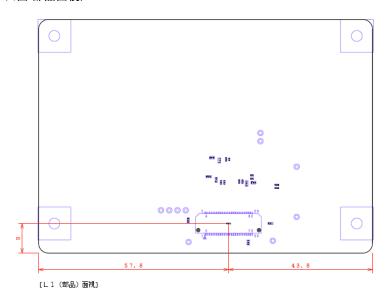

|    | 5.1.  | 基板寸法図14       |   |

#### 1. 概要

本仕様書は、GVI-4960 / NV017-D「GVIF2 デシリアライザ基板」のハードウェア仕様書です。「CXD4960 GVIF2 デシリアライザ基板」(以下本基板と表記)は、SONY 社 GVIF2 規格で送信されるシリアル映像信号を MIPI 信号に変換し、弊社 SVM-MIPI / SVM-06 基板に接続して使用するための変換基板です。本基板は従来の GVIF2 デシリアライザ基板(NV017-C)と比べて、システムクロック用のオシレータを実装できるパターンの追加、ESD 保護素子の追加等の対応をしています。ただし、標準仕様ではシステムクロック用オシレータは未実装となっています。

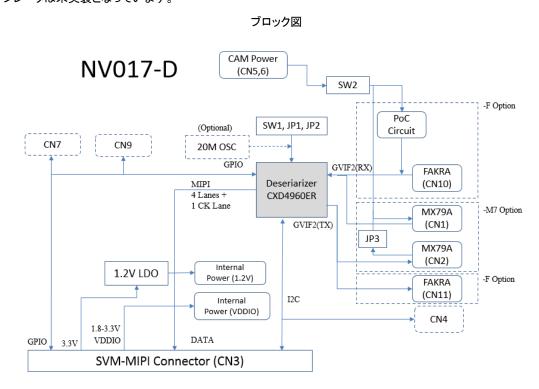

本基板のブロック図を示します。本基板は SONY 社デシリアライザ IC CXD4960ER・W を搭載しており、GVIF2 信号・> MIPI への変換、SVM・MIPI ボードと組み合わせた CXD4960ER のレジスタ設定および GVIF2 信号線を通した I2C / GPIO バックチャンネル通信が可能です。MIPI 信号の出力コネクタは弊社 SV シリーズ共通のインタフェースとなっており、SVM・MIPI 等と直結しての使用が可能です。GVIF2 信号の入力として FAKRA 規格のシングルエンド転送用コネクタと差動転送用コネクタが実装可能であり、車載用カメラとの接続に最適です。FAKRA 仕様の場合、入力 (RX) 側ポートは電源重畳 (PoC) にも対応します。コネクタ仕様は注文時にご指定下さい。

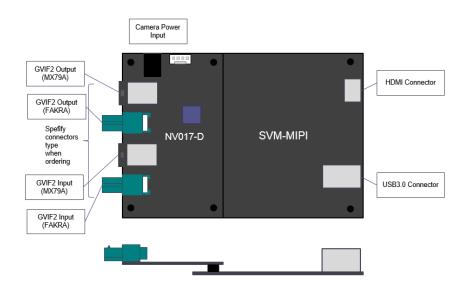

## ボード接続イメージ

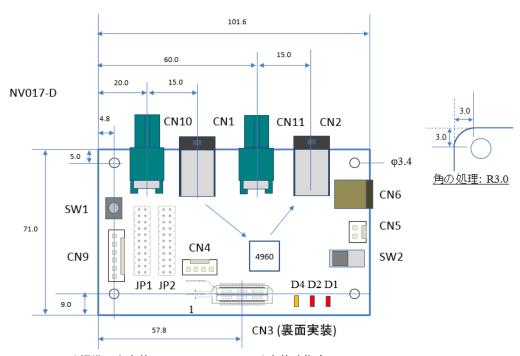

## 2. 基板形状

## 2.1. コネクタ配置図

- CN4, CN9 は標準で未実装、CN1-2, CN10-11 は実装時指定

- 詳しい部品寸法は図に反映されていません。

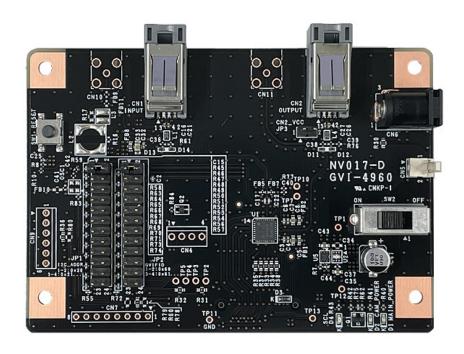

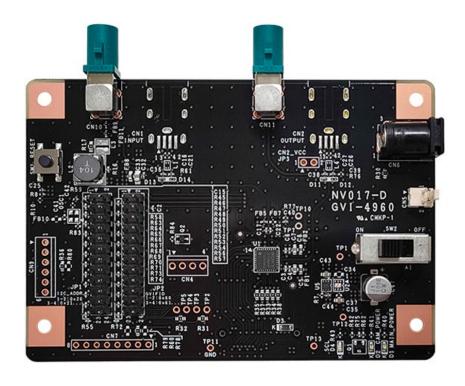

## 2.2. 基板写真

写真は MX79A コネクタ実装の -M7 仕様 (GVI-4960-M7) です。

写真は FAKRA コネクタ実装の -F 仕様 (GVI-4960-F) です。

## 3. 詳細

## 3.1. GVIF2 入力

本基板のデシリアライザ IC CXD4960 は入力を 1 系統 ( $G2RX\_SDP/N$ ,  $G2RX\_BCDP/N$ ) のみ備えて おり、本基板では 入力コネクタの切り替えを部品実装状態の違いによって行います。

差動コネクタ仕様の場合、C36, C40, R61, R77 を未実装として、CN1, C16, C21, L1, FB7 を実装します。 同軸コネクタ (FAKRA) 仕様の場合、L1, FB7 を未実装として、CN10, C36, C40, R61, R77 を実装します。 また、同軸コネクタ仕様の場合 PoC フィルタ回路(FB9, FB11, L2, R16, R17)も実装されます。C22 には差動コネクタ仕様の場合 180pF、同軸コネクタ仕様の場合は 100nF を実装しています。詳細は回路図を参照してください。

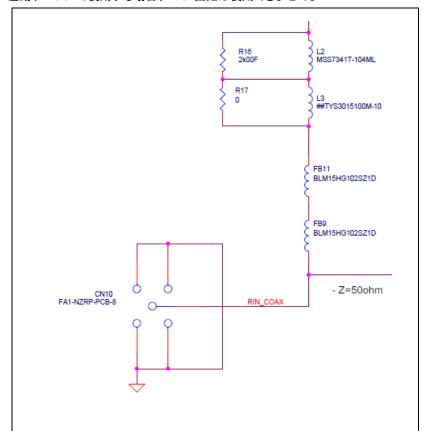

#### 3.2. PoC 回路

本基板を同軸ケーブルで使用する場合、PoC (Power over Coax) 回路によりケーブル上に電源を重畳することができます。本基板の PoC 回路を下記に示します。ただし、PoC 回路の転送性能は接続先の回路にも影響されるため、すべてのカメラの動作は保証できませんのでご留意ください。

差動ケーブルで使用する場合、PoC 回路は使用できません。

#### 3.3. GVIF2 出力

本基板のデシリアライザ IC CXD4960 は出力を 1 系統 (G2TX\_SDP/N) のみ備えており、本基板では出力コネクタの切り替えを部品実装状態の違いによって行います。GVIF2 出力を行わない場合、コネクタ CN2/CN11 は使用しません。

差動コネクタ仕様の場合、C38, C39, R76 を未実装として、CN2, C26, C27 を実装します。同軸コネクタ仕様の場合、C26, C27 を未実装として、CN11, C38, C39, R76 を実装します。詳細は回路図を参照してください。

#### 3.4. 電源

デシリアライザ IC CXD4960 の電源 (コア電源、IO 電源) は、CN3 を通して接続先ボード(SVM-MIPI 等)から供給します。コア電源の 1.2V となっており、本基板上の 1.2V レギュレータ (LDO) によりデシリアライザに対し電源を供給しています。3.3V 電源は CN3 のピンと直結になっているので、SVM-MIPI 以外の基板と接続する場合、安定した 3.3V を供給してください。IO 電源は 1.8V, 3.3V に対応しており、CN3 のVDDIO 電圧を供給しています。

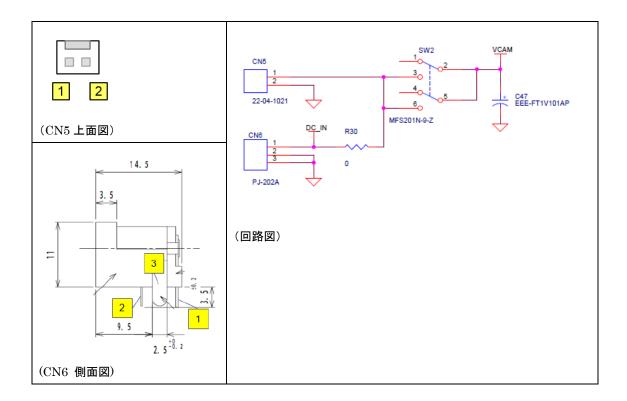

また、本基板では差動ケーブルまたは FAKRA ケーブルにカメラ用電源(VCAM)を出力することができます。この VCAM 電源はコネクタ CN5 または CN6 いずれかより供給し、FAKRA コネクタ仕様の場合 PoC 回路を通して同軸ケーブルに給電されます。差動ケーブルの場合、ケーブルの特定のピンに対して VCAM が接続されます。VCAM 電源と NV017-D 基板の内部電源とはコンデンサを通して DC 分離されているので、内部電源と VCAM 電源の投入順序は問いません。

#### 3.5. I2C バス、GVIFID

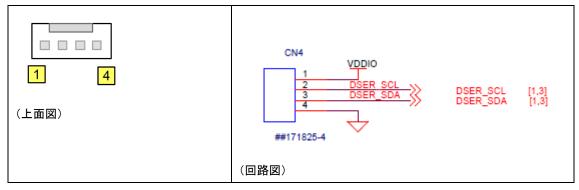

本基板のデシリアライザ IC (CXD4960) は I2C バスを有しており、IC 内の設定変更や GVIF2 ケーブルを通したシリアライザおよびターゲットデバイスとの I2C 通信機能を持ちます。本基板では、CXD4960 の I2C バスは  $4.7~\mathrm{k}\,\Omega$ で IO 電圧 (VDDIO) にプルアップした上、SVM-MIPI コネクタと直結しており、SVM-MIPI の標準機能により PC 等から I2C 通信が可能です。同時に、I2C バスは基板上の I2C 入出カコネクタ (CN4) に直結されているため、CN4 を実装することで外部デバイスとの接続や、外部マスタからの操作も可能になっています。

CXD4960 の I2C アドレスはジャンパ (JP1) により 11 種類に変更可能です。詳細については、ジャンパ設定の項を参照してください。同様に、GVIFID はジャンパ (JP2) により 11 種類に変更可能です。

## 3.6. コネクター覧表

| CN#  | 実装状態  | 名前              | 型番                 |

|------|-------|-----------------|--------------------|

| CN1  | 実装時指定 | GVIF2 入力 (差動)   | MX79A04HQ2         |

| CN2  | 実装時指定 | GVIF2 出力 (差動)   | MX79A04HQ2         |

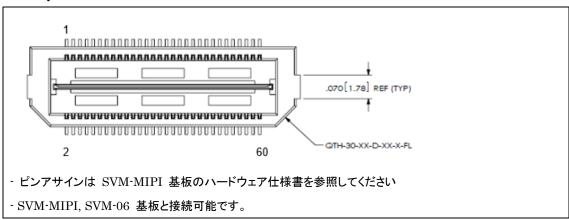

| CN3  |       | SVM-MIPI/06 接続用 | QTH-030-01-L-D-A   |

| CN4  | 未実装   | I2C 入出力         | 171825-4           |

| CN5  |       | カメラ電源入力1        | 22-04-1021         |

| CN6  |       | カメラ電源入力2        | PJ-202A            |

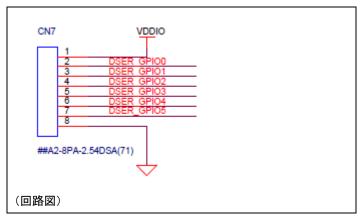

| CN7  | 未実装   | 拡張用コネクタ         | A2-8PA-2.54DSA(71) |

| CN9  | 未実装   | 拡張用コネクタ         | 171825-6           |

| CN10 | 実装時指定 | GVIF2 入力 (同軸)   | 0734035120         |

| CN11 | 実装時指定 | GVIF2 出力(同軸)    | 0734035120         |

- 実装状態は NV017-D に適用する

- 拡張用コネクタ (CN7, CN9) は複数ボードを使用した入力システムでの基板間通信、および将来の拡張用のコネクタです。

- カメラ電源入力コネクタ (CN5, CN6) は必要に応じてターゲットデバイス(カメラ)に供給する DC 電源を入力します。アプリケーションやシステムに応じて、いずれかのコネクタから電源を入力してください。カメラ電源はGVIF2 コネクタに出力されるのみであり、NV017-D 基板内部では使用していません。必要な電源容量はターゲットデバイスに依存します。カメラ電源の入力電圧は 16V 以下としてください。

- I2C 入出力コネクタ (CN4) はデシリアライザ IC (CXD4960ER) の I2C バスに直結されています。

## 3.7. コネクタ詳細

回路図中 ## で始まる部品は未実装部品を示します。

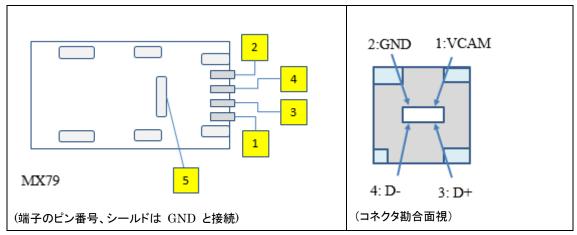

•CN1, CN2 (MX79A04HQ2)

GVIF2 デシリアライザ基板 (NV017-D) ハードウェア仕様書 第4版

- 実装されるコネクタのキータイプは注文時の指定によります。

#### •CN3 (QTH-030-01-L-D-A)

#### • CN4 (171825-4 / TE Connectivity)

•CN5 (22-04-1021 / Molex), CN6(PJ-202A)

•CN7 (A2-8PA-2.54DSA(71))

- DSER\_GPIO0-5: デシリアライザ CXD4960 の IO0-5 と接続

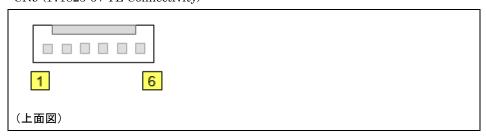

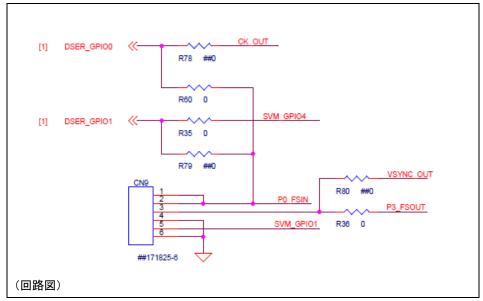

- •CN9 (171825-6 / TE Connectivity)

- P0\_FSIN: CN3 の 2 ピンと接続

- P3\_FSOUT: CN3 の 10 ピンと接続

- SVM\_GPIO1: CN3 の 4 ピンと接続

- SVM\_GPIO4: CN3 の 22 ピンと接続

- VSYNC\_OUT: CN3 の 43 ピン、基板上 TP13 と接続

- CK\_OUT: CN3 の 49 ピンと接続

- DSER\_GPIO0-1: デシリアライザ CXD4960 の IO0-1 と接続

- 抵抗実装の変更で、GPIO0-1 と SVM 基板、CN9 の間の接続を変更することができます。

#### 3.8. スイッチ

本基板にはリセットスイッチとして SW1 が実装されています。SW1 を押下すると、CXD4960 の CE ピンが L 状態になります。

## 3.9. ジャンパ設定

· JP1

JP1 は CXD4960 の I2C アドレスを指定するジャンパです。ジャンパピンにより、下表のいずれか 1 つを選択してください。システムクロック用オシレータを実装する場合は、13-14 短絡(0x26) または 15-16 短絡 (0x27) としてください。

GVIF2 デシリアライザ基板 (NV017-D) ハードウェア仕様書 第4版

| 短絡ピン  | I2C アドレス (7 bit) |

|-------|------------------|

| 1-2   | 0b0100000 (0x20) |

| 3-4   | 0b0100001 (0x21) |

| (中略)  |                  |

| 21-22 | 0b0101010 (0x2A) |

出荷時は 3-4 短絡状態となります。

#### · JP2

JP2 は CXD4960 の GVIFID を指定するジャンパです。ジャンパピンにより、下表のいずれか 1 つを選択してください。

| 短絡ピン  | GVIFID            |

|-------|-------------------|

| 1-2   | 0b01100000 (0x60) |

| 3-4   | 0b01100001 (0x61) |

| (中略)  |                   |

| 21-22 | 0b01101010 (0x6A) |

出荷時は 1-2 短絡状態となります。

## 3.10. LED インジケータ

本基板には3つのLEDが実装されています。それぞれの機能は下表の通りです。

| LED# | 名前         | 機能                           |

|------|------------|------------------------------|

| D1   | MAIN_POWER | 3.3V 電源 が供給されていれば点灯します。      |

| D2   | CAM_POWER  | カメラ電源(VCAM)が供給されていれば点灯します。   |

| D4   | SCL        | デシリアライザの SCL ピンが L のとき点灯します。 |

## 4. 主要諸元

| 項目         | 値               | 備考                        |

|------------|-----------------|---------------------------|

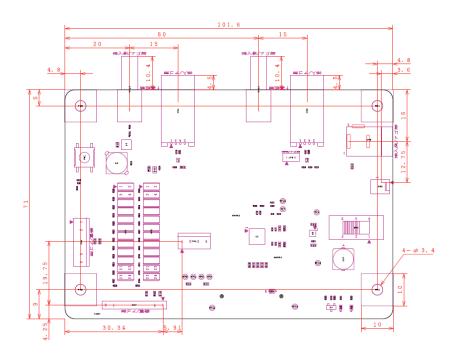

| 基板寸法       | 71.0 x 101.6 mm | コネクタを含まない値                |

| デシリアライザ用電源 | DC +3.3V        | CN3 経由、SVM-MIPI 等キャプチャボード |

|            |                 | (3.3V 出力)から供給、コア電源は基板上    |

|            |                 | LDO で 1.2V に降圧            |

GVIF2 デシリアライザ基板 (NV017-D) ハードウェア仕様書 第4版

| 項目     | 値                  | 備考                        |

|--------|--------------------|---------------------------|

| IO 電源  | DC +3.3V / 1.8V    | CN3 経由、SVM-MIPI 等キャプチャボード |

|        |                    | (VDDIO)から供給               |

| カメラ用電源 | DC +16V / 300mA 以下 | CN5 または CN8 コネクタから供給      |

|        |                    | CN6 実装で AC アダプタに対応        |

| 画像入力   | GVIF2 規格           | MX79A コネクタもしくは FAKRA コネクタ |

|        |                    | FAKRA コネクタの場合は PoC 対応     |

| 画像出力   | MIPI CSI-2         | CN3 に出力                   |

|        | 1-4 Lanes + CLK    | インタフェースは SVM-MIPI 等に対応    |

|        |                    | レーン数は 1-4 Lane 設定可能       |

| シリアル通信 | 12C                | I2C バスは CN3 および CN4 に出力   |

|        |                    |                           |

- 上記仕様は型番 NV017-D にのみ適用されます。

- SVM-MIPI 基板と接続する場合、SVM-MIPI 側を Continuous Clock 設定にする必要があります。

## 5. Appendix

## 5.1. 基板寸法図

(部品面/部品面視)

## (半田面/部品面視)