# GEO GW5410/5210 ISP 基板 (NV065-A) ハードウェア仕様書

第3版

# [注意]

本基板の IO 電圧は 1.8V 固定です。 接続する基板の IO 電圧は必ず 1.8V に設定して下さい。

株式会社ネットビジョン

#### 株式会社ネットビジョン

#### NV065-A GEO GW5410/5210 ISP 基板 ハードウェア仕様書 第2版

#### 改訂履歴

| 版数  | 日付         | 内容                           | 担当 |

|-----|------------|------------------------------|----|

| 第1版 | 2022/04/18 | 初版作成                         | 折笠 |

| 第2版 | 2022/06/09 | 記述修正                         | 折笠 |

| 第3版 | 2022/08/19 | IO 電圧注意書き追加、CN1-3 コネクタピン配置追加 | 折笠 |

|     |            |                              |    |

# 目次

| 1.    | 概要3                      |

|-------|--------------------------|

| 2.    | 基板形状4                    |

| 2.1.  | 基板寸法図4                   |

| 2.2.  | 基板写真5                    |

| 3.    | 基板詳細6                    |

| 3.1.  | ボード接続図(Parallel 接続)      |

| 3.2.  | ボード接続図(MIPI 接続) <b>7</b> |

| 3.3.  | コネクター覧表                  |

| 3.4.  | CN1、CN2、CN3 ピン配置10       |

| 3.5.  | スイッチ設定11                 |

| 3.6.  | LED インジケータ               |

| 3.7.  | FT4222 モジュール             |

| 3.8.  | GPIO                     |

| 3.9.  | ISP ファームウェア              |

| 3.10. | I2C Slave Address        |

| 3.11. | 電源回路構成                   |

| 4.    | 主要諸元18                   |

| 5.    | Appendix                 |

| 5.1.  | 基板寸法図19                  |

#### 1. 概要

本仕様書は NV065-A 基板のハードウェア仕様書です。NV065-A 基板(以下本基板と表記)は、MIPI の入出力とパラレル出力を持ち、入力された映像を GEO 社 GW5 ISP を介して画像処理を行い、出力するための基板です。複数のコンフィギュレーションに柔軟に対応可能な回路構成となっており、現状 2 種のコンフィグレーションを持ちます。基板品番 NV065-A-E は ISP として GW5210 を、NV065-A-G は ISP として GW5410 を搭載します。NV065-A-E はローンチカスタマー向けの仕様となっておりますので、通常は NV065-A-G をご選択頂く形になります。ISP をピンコンパチの GW5 シリーズから選択頂くことも可能です。ISP のコア電源の AVS 回路の定数は、使用される ISP 型番に応じて調整を致します。

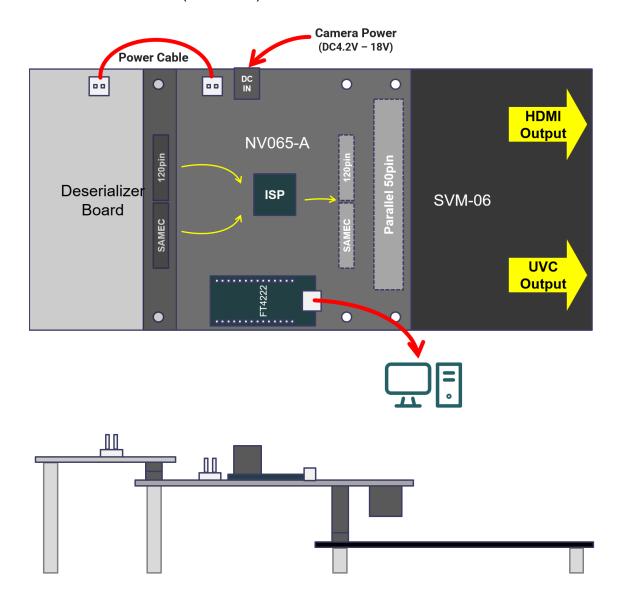

#### NV065-A Block Diagram CN1: SAMTEC OSH-060-01-L-D-A 4Lane MIPI x2 for NV SerDes Boards CN5 **DIP Switch Settings** GPIO 5V 3.3V 1.8V 1.1.2: GWS 12C Slave Address Select 3: Connect GW5 Reset with SVM Reset Output 4: Connect GW5 Reset to GND through IX ohm 5.6: Connect Deserializer 12C Bus with SVM 7,8: Connect GW5 12C Slave Bus with SVM MIPI D5-D8, CLK2 Tr OUT FET BusSW SVM\_I2C SVM\_GPIO CN4 DC IN IO Expander DC/DC MIPI\_RX1 I2C\_0 (Master) MIPI\_RX0 TCA9534PWR SVM Load Switch 3.3V 12C ADDR: 0x22 /RESET USB Mini-B Connector FTDI I2C\_2 (Slave) UMFT4222EV Quad Bus DC/DC 0.9V SPI\_1 (Slave) Module Quad Bus VDD SRX\_VDDA STX\_VDDA ISP STX/STX0/ STX1\_VDDPLL SPI NOR Flash **GEO** SPI\_0 (Master) IO VDD0-2 DC/DC 1.8V VDD\_PLL SX\_VDDHA GW5210/5410 24MHz OSC ECS-2520MV-240-BN-TR VDD\_QPS **Boot Strap** I2C 1 Boot Mode (SPI0\_MOSI/GPO0): 00: Boot from SNOR, if failure from I2C2 pins 10: Boot from I2C2 pins TPs & JTAG 67996-120HLF JTAG IOVDD2 Voltage (GPO2/GPO1): 00: 1.8V IOVDD1 Voltage (GPO5/GPO4): 00: 1.8V CLK1 VSYNC, PCLK Adjustable CN3: USECONN C-00086 CN2: SAMTEC QTH-060-04-L-D-A 16-bit Parallel for SVM-03 4Lane MIPI x2 for SVM-06

ブロック図

本基板は映像入力元として、2 系統の MIPI 入力を持ち、各々が ISP に接続されています。MIPI 入力コネクタ(CN1)は、弊社製各種デシリアライザ基板に接続し、使用されます。映像出力先として、MIPI と 16-bit Parallel の 2 系統を備えています。MIPI 出力コネクタ(CN2)は弊社製 SVM-06 基板と接続され、16-bit Parallel 出力コネクタ(CN3)は弊社製 SVM-03 基板と接続されます。両コネクタは排他接続となります。

本基板の動作電源は CN4 の DC ジャックより供給され、内部の降圧回路を介して各種 IC へと供給されます。

同時に CN4 より入力された電圧は、FET を介して CN5 へと出力され、CN1 に接続されたデシリアライザ基板のカメラ電源となります。FET の Gate は SVM ボードから制御されます。ISP の設定や FW 更新等には基板上に取り付けられる FTDI 社 FT4222 モジュールに、USB ケーブルで接続された PC から行います。

### 2. 基板形状

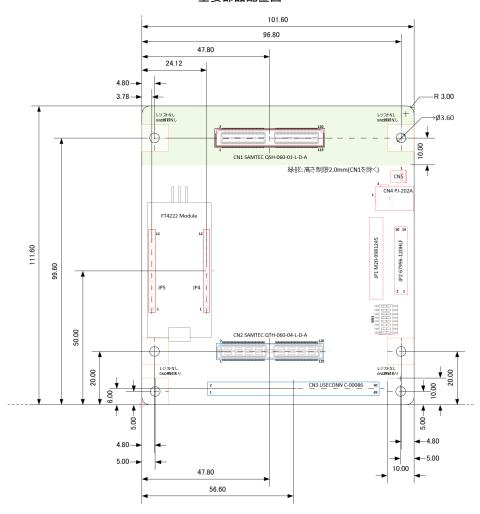

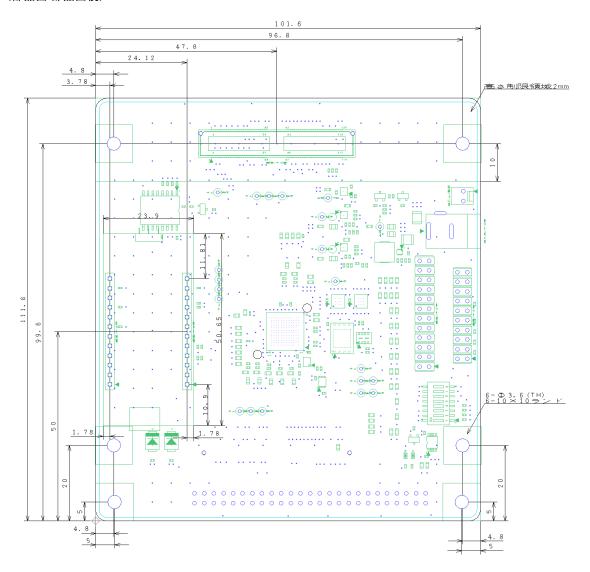

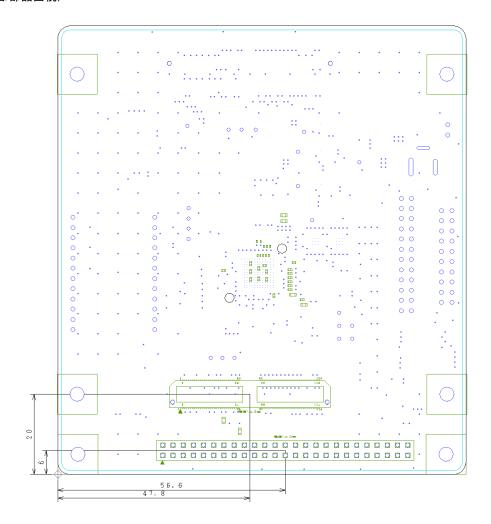

#### 2.1. 基板寸法図

本基板の基板寸法図及び主要部品配置図を下図に示します。コネクタのピン番号、ピンアサインは「コネクタ詳細」の項で示します。

主要部品配置図

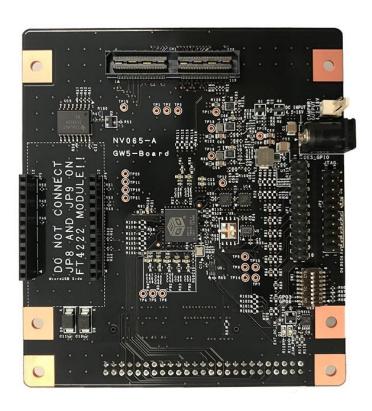

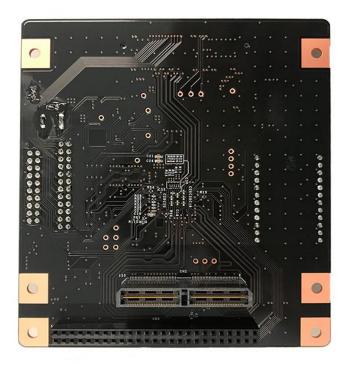

# 2.2. 基板写真

#### 3. 基板詳細

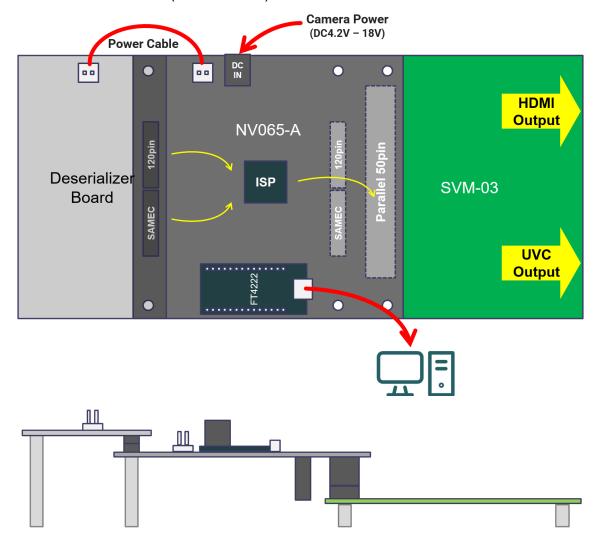

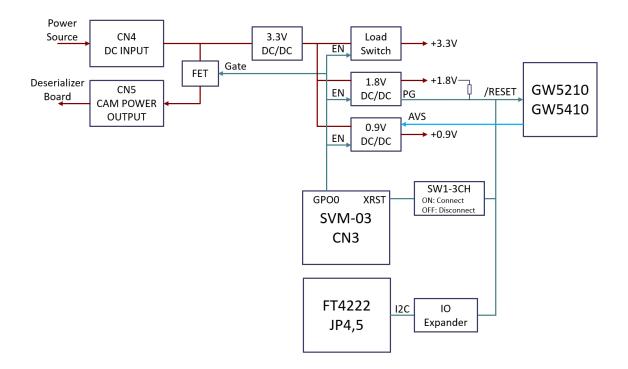

#### 3.1. ボード接続図(Parallel 接続)

上図は、SVM-03と接続し、映像出力インターフェースとして 16-bit Parallel を使用する場合の接続図です。

#### SVM-03 VR2 の可変抵抗を調整し、VDDL(IO 電圧)は必ず 1.8V に設定して下さい。

本基板の電源として DC ジャック(CN4)に AC アダプタを接続します。入力された電源は、FET を介して CN5 からデシリアライザ基板のカメラ電源コネクタへと接続します。そのため、入力する電圧は、カメラの電源電圧と一致させる必要があります。入力電圧は、4.2V から 18V の間となるようにしてください。

16-bit Parallel 出力コネクタ(CN3)は SVM-03 と接続され、映像信号を SVM-03 へ出力します。

${

m FT4222}$  モジュールと PC は、 ${

m Micro~USB}$  ケーブルで接続し、 ${

m FW}$  の書き込みや画質調整には、 ${

m GEO}$  社製ツールを使用します。

SVM-03からの映像出力は、HDMI 出力もしくは UVC 出力のどちらかを、SVM-03の基板上の DIPSW(SW2) で選択します。#1、8 ON -> UVC Mode, #1 ON -> HDMI Mode

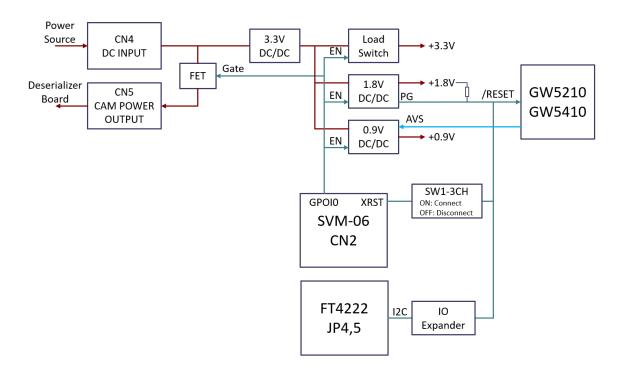

#### 3.2. ボード接続図(MIPI 接続)

上図は、SVM-06と接続し、映像出カインターフェースとして MIPI を使用する場合の接続図です。

#### SVM-06 JP1 は必ず 5-6pin 間をショートさせ、IO 電圧を 1.8V に設定して下さい。

本基板の電源として DC ジャック(CN4)に AC アダプタを接続します。入力された電源は、FET を介して CN5 からデシリアライザ基板のカメラ電源コネクタへと接続します。そのため、入力する電圧は、カメラ電源電圧と一致させる必要があります。入力電圧は、4.2V から 18V の間となるようにしてください。

MIPI 出力コネクタ(CN2) は SVM-06 と接続され、映像信号を SVM-06 へ出力します。

${

m FT4222}$  モジュールと PC は、Micro USB ケーブルで接続し、FW の書き込みや画質調整には、GEO 社製ツールを使用します。

SVM-06 からの映像出力は、HDMI mode における UVC 同時出力に対応しています。 (SW2:全て OFF で HDMI コネクタと USB コネクタの両方から映像を出力します。)

# 3.3. コネクター覧表

| CN# | 用途                      | 型番                      | ピン配置                                                            |

|-----|-------------------------|-------------------------|-----------------------------------------------------------------|

| CN1 | MIPI 4-Lane Dual Input  | SAMTEC QSH-060-01-L-D-A | 2                                                               |

|     | 弊社デシリアライザ基板の            |                         |                                                                 |

|     | MIPI コネクタが接続されるた        |                         | 1 119                                                           |

|     | め、SVM-06 CN4 と互換性を      |                         |                                                                 |

|     | 持ちます。                   |                         |                                                                 |

| CN2 | MIPI 4-Lane Dual Output | SAMTEC QTH-060-04-L-D-A | 2,000,000,000,000,000,000,000,000,000,0                         |

|     | SVM-06 CN4 と接続されるた      |                         |                                                                 |

|     | め、弊社デシリアライザ基板の          |                         | 100000000000000000000000000000000000000                         |

|     | MIPI コネクタと互換性を持ち        |                         | ※基板上面から透過して見た図                                                  |

|     | ます。                     |                         |                                                                 |

| CN3 | 16-bit Parallel Output  | USECONN C-00086         | 2<br>1 50                                                       |

|     | SVM-03 CN4 と接続されるた      | or equivalent           | ※基板上面から透過して見た図                                                  |

|     | め、弊社デシリアライザ基板の          |                         |                                                                 |

|     | パラレルコネクタと互換性を持          |                         |                                                                 |

|     | ちます。                    |                         |                                                                 |

| CN4 | Power Input             | CUI Devices PJ-202A     | Φ 2.1mm, Center Plus  MATING PLUG  Jack Insertion Depth: 9.0 mm |

| CN5 | Power Output            | Molex 22-04-1021        |                                                                 |

#### 株式会社ネットビジョン NV065-A GEO GW5410/5210 ISP 基板 ハードウェア仕様書 第 2 版

| CN#         | 用途                        | 型番                                  | ピン配置                                                                          |

|-------------|---------------------------|-------------------------------------|-------------------------------------------------------------------------------|

|             |                           |                                     | CAMPWR:<br>0UTPUT<br>4. 2-18V<br>2 0 1<br>CN5 ▲                               |

| JP1         | GPIO Connection Selection | HARWIN M20-9981245<br>or equivalent | JP1  2  1  0  0  0  0  0  0  0  0  0  0  0  0                                 |

| JP2         | JTAG                      | Amphenol 67996-120HLF               | 19 1<br>20 JTAG 2                                                             |

| JP4,<br>JP5 | FT4222 Module             | USECONN FH-1x12SG/RH                | FT4222 Module  12 12 0  13 12 12 0  14 15 15 15 15 15 15 15 15 15 15 15 15 15 |

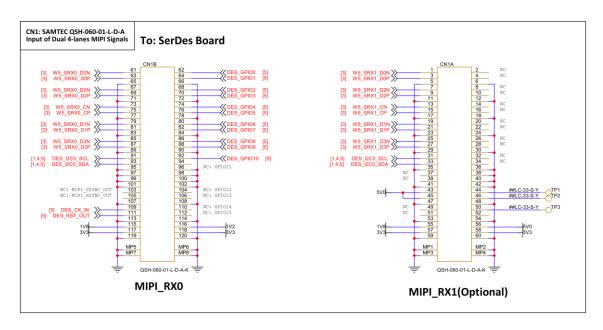

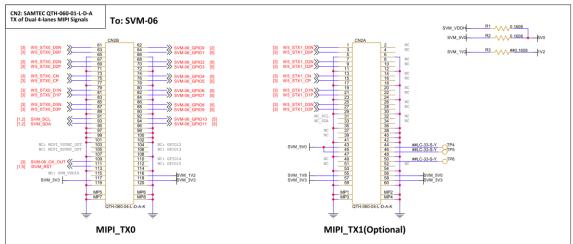

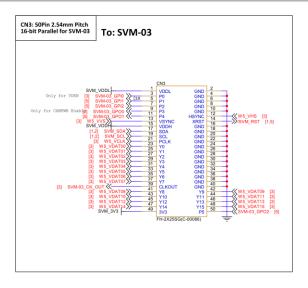

#### 3.4. CN1、CN2、CN3 ピン配置

# 3.5. スイッチ設定

本基板には ISP 設定用スイッチ SW1 が実装されています。SW1 の機能は下表の通りです。

| SW# | 名前           | 出荷状態 | 機能                                           |

|-----|--------------|------|----------------------------------------------|

| 1   | W5_GPO6      | OFF  | SNOR リカバリーモードで起動させる際の I2C Slave Address を    |

| 2   | W5_GPO3      | OFF  | 設定する Bootstrap の Hi/Lo を切り替えます。              |

|     |              |      | ON: Hi, OFF: Lo                              |

|     |              |      |                                              |

|     |              |      | [W5_GPO6] – [W5_GPO3]                        |

|     |              |      | Lo – Lo : 0xD8 (default)                     |

|     |              |      | Lo – Hi : 0xDA                               |

|     |              |      | Hi – Lo: 0xDC                                |

|     |              |      | Hi – Hi : 0xDE                               |

| 3   | 1V8_REG_PG   | ON   | ISP のリセットピンを/SVM_RST と接続します。この設定により、         |

|     |              |      | SVM ボード側から、ISP をリセット状態にすることが可能になりま           |

|     |              |      | す。ISP 及びカメラへの電源供給後に ISP のリセットを解除するた          |

|     |              |      | め、出荷状態では ON になっています。                         |

|     |              |      | ON: SVM ボードから ISP をリセット可能                    |

|     |              |      | OFF: SVM ボードから ISP をリセット不可                   |

| 4   |              | OFF  | $ISP$ のリセットピンを $1k\Omega$ でプルダウンします。この設定により、 |

|     |              |      | ISP が常にリセット状態になります。                          |

|     |              |      | ON: ISP が常にリセット状態                            |

|     |              |      | OFF: 通常状態                                    |

| 5   | DES_I2C0_SCL | OFF  | デシリアライザ基板の I2C バスを SVM ボードに接続します。            |

| 6   | DES_I2C0_SDA | OFF  | ※デシリアライザの設定は ISP から行うため、通常使用しません。            |

|     |              |      | ON: I2C バスを SVM ボードに接続                       |

|     |              |      | OFF: I2C バスを SVM ボードから切断                     |

| 7   | FT_I2C_SCL   | OFF  | ISP の I2C Slave バスを SVM ボードに接続します。           |

| 8   | FT_I2C_SDA   | OFF  | ON: I2C バスを SVM ボードに接続                       |

|     |              |      | OFF: I2C バスを SVM ボードから切断                     |

#### 3.6. LED インジケータ

| LED# | 名前        | 機能                                  |

|------|-----------|-------------------------------------|

| D1   | EXT_DC_IN | DC ジャックに電源が供給された時に点灯します。            |

| D2   | CAM_PWR   | SVM の GPIO からカメラ電源供給が有効化された時に点灯します。 |

#### 3.7. FT4222 モジュール

本基板の JP4、JP5 には FTDI 社 FT4222 モジュール(UMFT4222EV)が挿入されます。挿入には向きがありますので、基板シルク「Micro USB Side」側に Micro USB コネクタが来るように挿入する必要があります。 FT4222 モジュールは IO 電圧用に 1.8V の電圧レギュレータを内蔵していますが、本基板の IO 電圧は 1.8V のため、本基板と接続する際は使用しません。FT4222 の VCC 電源も、本基板から 3.3V を供給します。そのため、モジュール上の JP8、JP9 を必ず取り外した状態で使用します。JP2、JP3 は動作モードの設定用ジャンパーピンです。共に Lo に設定するため、2-3 間をショートさせる必要があります。 弊社が FT4222 モジュールを同梱して出荷する場合、上記設定は反映された状態で出荷されます。

#### 3.8. GPIO

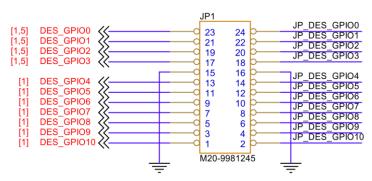

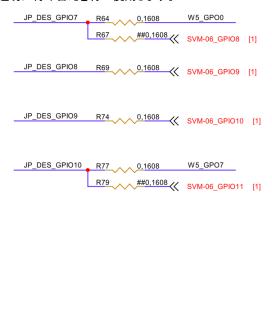

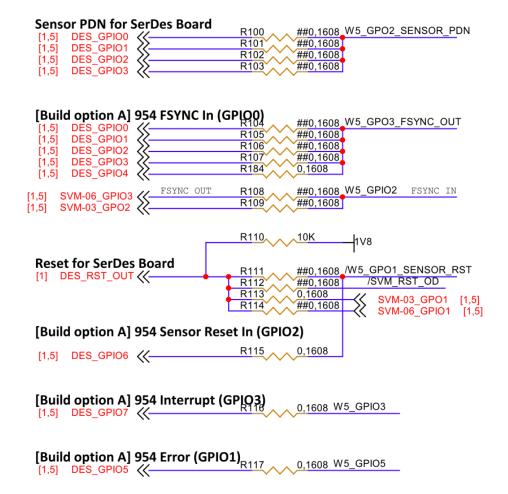

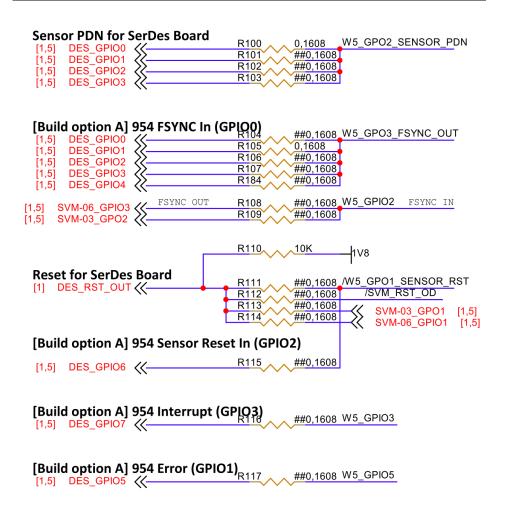

本基板は、デシリアライザ基板上のデシリアライザ IC の GPIO への接続先を、ISP の各 GPIO ピン、またはSVM ボードの各 GPIO ピンから選択可能な回路構成になっています。

接続経路は、デシリアライザ基板へ繋がる GPIO(DES\_GPIO[0:10])へ  $0\Omega$ 抵抗経由で接続される経路と、JP1 を通して接続される経路の 2 種類があります。JP1 を通して接続される経路は、出荷状態では全てのジャンパーピンが取り外されているため、切断状態になっています。

#### ◆接続経路: JP1 経由

デシリアライザ基板へ繋がる GPIO(DES\_GPIO[0:10])は、JP1 を通して JP\_DES\_GPIO[0:10]に接続されます。 出荷時は、JP1 の全てのジャンパーピンは取り外されており、DES\_GPIO\*及び JP\_DES\_GPIO\*間は切断されています。

$JP\_DES\_GPIO[0:10]$ と、ISP の各 GPIO ピン及び SVM ボードの GPIO との接続は、 $0\Omega$ 抵抗を介して行います。1608 サイズの抵抗となっておりますので、必要に応じて適切に付け替えを行い使用します。

#### ◆接続経路: 0Ω抵抗経由

$0\Omega$ 抵抗で直接接続される経路は、NV065-A-E と NV065-A-G とで異なる構成となっています。

● NV065-A-E 基板は、弊社 FPI-954-HF ボード(FPD Link III DS90UB954 デシリアライザ搭載)への接続 を前提とした回路構成となっています。

| Deserializer Side | ISP Board Side      | Note                      |

|-------------------|---------------------|---------------------------|

| DES_GPIO4         | W5_GPO3_FSYNC_OUT   | To 954 FSYNC Input        |

| DES_GPIO5         | W5_GPIO5            | To 954 Error Output       |

| DES_GPIO6         | /W5_GPO1_SENSOR_RST | To 954 Sensor Reset Input |

| DES_GPIO7         | W5_GPIO3            | To 954 Interrupt Input    |

● NV065-A-G 基板は、GEO 社 Evaluation Board に近い回路構成となっています。

| Deserializer Side | ISP Board Side     | Note |

|-------------------|--------------------|------|

| DES_GPIO0         | W5_GPO2_SENSOR_PDN |      |

| DES_GPIO1         | W5_GPO3_FSYNC_OUT  |      |

#### 3.9. ISP ファームウェア

本基板を使用するためには、事前に ISP のファームウェアを書き込む必要があります。ファームウェアの書き込みの際は、FT4222 モジュールと PC を接続し、GEO 社の書き込みツールを使用してください。ツールの詳細や、使用方法については、GEO 社の公式ドキュメントをご確認ください。本基板は GEO 社 Evaluation Board と同様の構成を取っているため、ファームウェア書き込み時の ISP へのリセットは FT4222 から自動的に行われます。そのため、DIPSW やジャンパーピンでの設定は特に不要です。

[参考] 弊社での書き込み時は、以下コマンドで書き込みを行っております。(2022/04/18 時点)

.¥flash\_util.exe -w0 -tw5 <file path of firmware>

#### 3.10. I2C Slave Address

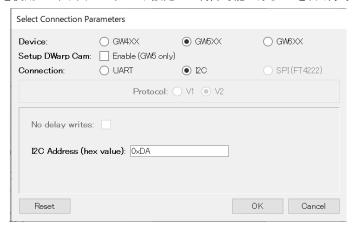

ISP の Host からの制御用 I2C Slave Address は 0xDA(8bit)となっています。

GEO 社 ISPTune を使用して、下図のパラメータ設定にて制御可能であることを、出荷時に確認しています。

#### 3.11. 電源回路構成

♦SVM-03 (Parallel Output from ISP)

#### $\diamond$ SVM-06 (MIPI Output from ISP)

# 4. 主要諸元

| 項目      | 値                      | 備考                     |

|---------|------------------------|------------------------|

| 基板寸法    | 101.6 x 111.6 mm       |                        |

| 供給電源    | DC 4.2-18V             | CN5 経由でカメラ電源を兼ねる       |

|         | Center Plus,           | 内部電源はボード上レギュレータにより生成   |

|         | Ф2.1mm / 5.5mm Plug    |                        |

| ISPコア電源 | DC +0.9V               | AVS 回路により ISP から電圧動的制御 |

| IO 電圧   | DC +1.8V               |                        |

| 画像入力    | 2x MIPI CSI-2          | CN1 より入力               |

|         | 4-lane 1.5Gbps/lane    |                        |

| 画像出力    | MIPI:                  | MIPI: CN2 から出力         |

|         | 2x MIPI CSI-2          |                        |

|         | 4-lane 1.5Gbps/lane    | Parallel: CN3 から出力     |

|         |                        |                        |

|         | Parallel:              |                        |

|         | 1x 16-bit Parallel     |                        |

|         | 150MHz Interface Clock |                        |

| シリアル通信  | I2C                    | 内部配線は回路図参照             |

|         | SPI                    |                        |

# 5. Appendix

# 5.1. 基板寸法図

(部品面/部品面視)

[L]〈部品〉面視]

#### (半田面/部品面視)

[L] (部品)面視]